UNIST 김정환·정창욱 교수팀, 전하 이동도 최대 30배 과대평가 원인 규명

전극 기하학적 구조 유발 프린지 전류가 원인·소자 설계 표준 제시, ACS Nano 게재

반도체 개발 과정에서 연구자들의 나침반 역할을 해온 성능 평가 지표에 심각한 오류가 숨어 있다는 사실이 밝혀졌다.

UNIST 반도체소재·부품대학원 김정환·정창욱 교수팀은 반도체 소자의 주요 성능 지표인 '전계 효과 전하 이동도(Field-Effect Mobility)'가 소자 구조에 따라 실제보다 최대 30배까지 부풀려져 측정될 수 있음을 규명하고, 이 문제를 해결할 반도체 소자 구조 설계 표준을 제시했다고 3일 밝혔다.

연구진 (좌측부터) 김정환 교수, 정창욱 교수, 김수현 연구원(제1저자), 이영준 연구원(제1저자). UNIST 제공

전하 이동도는 반도체 내부에서 전하(전류)가 얼마나 빠르고 효율적으로 움직이는지를 나타내는 지표다. 이 수치가 클수록 소자가 더 빠르게 작동하고 전력 소모는 줄어들기 때문에, 고성능 반도체 칩 개발의 성패를 가늠하는 중요한 척도로 여겨진다.

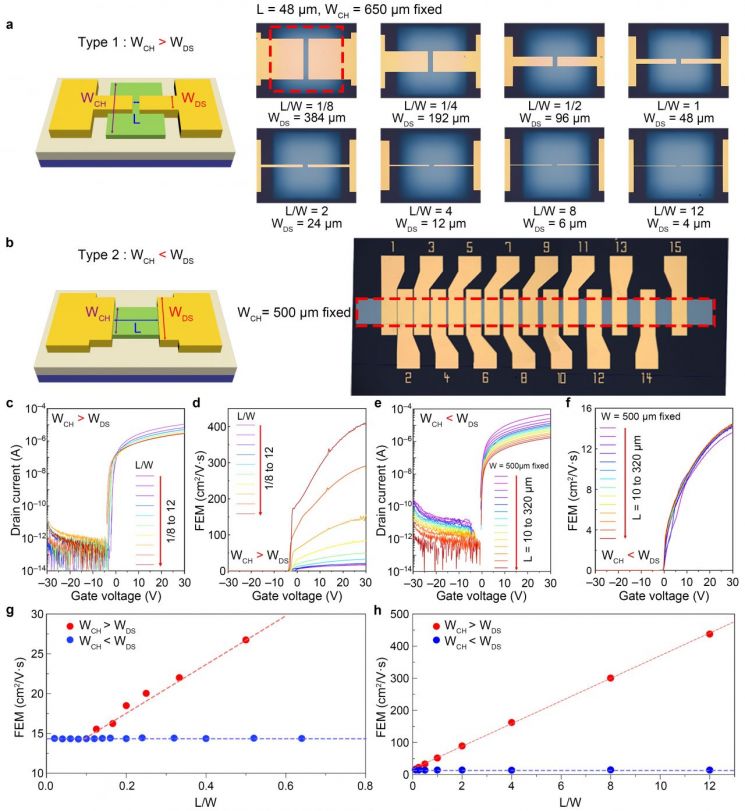

연구에 따르면, 이 전하 이동도는 산화물 박막트랜지스터(Thin-Film Transistor) 반도체 소자의 기하학적 구조에 따라 최대 30배 이상 과대 측정될 수 있다.

연구진은 그 원인으로 '샛길'로 흐르는 프린지 전류(fringe current)를 지목했다. 박막트랜지스터 소자에서 전류는 '소스 전극'으로 들어와 정식 통로인 '채널'을 거쳐 '드레인 전극'으로 빠져가는 형태다. 그런데 채널 폭이 전극보다 훨씬 넓을 경우, 전류가 전극 바로 아래의 본래 통로뿐만 아니라 전극 바깥의 넓은 주변부(샛길)로까지 퍼져 흐르는 '프린지 전류'가 생기는 것이다. 측정 장비는 이 모든 전류를 합산해 성능을 계산하므로 실제보다 부풀려진 결과가 나오게 된다.

전하이동도를 차가 꽉 막힌 고속도로에서 자동차의 평균 속도에 비유한다면, 프린지 전류는 갓길로 마구 달리는 자동차까지 합산시켜 전체 평균 속도가 실제보다 훨씬 빠른 것처럼 착각하게 만드는 효과를 내는 것이다.

연구팀은 이 문제를 해결하기 위한 박막트랜지스터 소자 설계 표준도 제시했다. 채널 폭을 전극 폭보다 좁게 설계하거나, 부득이한 경우에는 전극의 폭이 전체 소자 길이(L)보다 12배 이상 크도록(L/W ≤ 1/12) 설계해야 한다는 것이다.

이 기준을 따랐을 때 프린지 전류의 영향이 거의 사라져, 실제 이동도와 측정 이동도의 차이가 없어지고 정확한 성능 측정이 가능함을 실험과 시뮬레이션을 통해서 입증했다.

또 홀 이동도(Hall mobility)라는 지표를 함께 측정해 전계 효과 이동도와 교차 검증할 것을 권고했다. 홀 이동도는 완성된 소자가 아닌 반도체 박막 물질 자체의 고유한 전기적 특성을 측정하는 방식으로, 반도체 소자의 기하학적 구조로 인해 발생하는 오류에서 자유롭다.

김정환 교수는 "소자 성능 측정 오류는 성능이 과대 평가된 소재를 유망한 차세대 기술로 오인하게 해 연구 역량을 허비하게 하거나, 객관적인 기술 비교를 불가능하게 해 반도체 산업 전체의 발전을 저해할 수 있다"며 "이를 해결할 수 있는 글로벌 표준을 제시했다는 점에서 의미 있는 연구"라고 말했다.

채널과 전극 구조별 박막 트랜지스터(TFT)의 전하 이동도 비교.

이번 연구는 미국화학학회에서 발간하는 나노분야 학술지인 에이씨에스나노(ACS Nano)에 10월 21일 출판됐다.

연구 수행은 과학기술정보통신부 한국연구재단, 산업통상자원부 등의 지원을 받아 이뤄졌다.

영남취재본부 김철우 기자 sooro97@asiae.co.kr

<ⓒ투자가를 위한 경제콘텐츠 플랫폼, 아시아경제(www.asiae.co.kr) 무단전재 배포금지>